# ENGINEERING & MANAGEMENT EXAMINATIONS, DECEMBER - 2008 COMPUTER ORGANIZATION & ARCHITECTURE

### SEMESTER - 1

| Time: 3 Hours] |  | [ Full Marks : 70 |

|----------------|--|-------------------|

| Inne . O Hours |  |                   |

## GROUP - A

|    |                                                                           |                                       | ( Multiple (                    | Choice T | уре 9 | questions)                     |

|----|---------------------------------------------------------------------------|---------------------------------------|---------------------------------|----------|-------|--------------------------------|

| 1. | Cho                                                                       | ose th                                | : 10 × 1 = 10                   |          |       |                                |

|    | i)                                                                        | 1 nibble is equal to                  |                                 |          |       |                                |

|    |                                                                           | a)                                    | 4 bits                          |          | b)    | 8 bits                         |

|    |                                                                           | <b>c</b> )                            | 12 bits                         |          | d)    | 16 bits.                       |

|    | ii)                                                                       | 364                                   | (8) =(1                         | 0)       | •.    |                                |

|    |                                                                           | a)                                    | 222                             |          | b)    | 102                            |

| ê  |                                                                           | c)                                    | 244                             |          | d)    | 230.                           |

|    | iii)                                                                      | iii) 6B9 ( Hexadecimal ) = ( Binary ) |                                 |          |       |                                |

|    |                                                                           | a)                                    | 11010111001                     |          | b)    | 01010111010                    |

|    | •                                                                         | c)                                    | 11110011001                     |          | d)    | 101010101010.                  |

|    | iv)                                                                       | Valu                                  | the of $(a + b'c')'$ . $(ab' +$ | abc ) =  | ••••• |                                |

|    |                                                                           | a)                                    | zero                            |          | b)    | one                            |

|    |                                                                           | <b>c</b> )                            | а                               |          | d)    | ab.                            |

|    | v)                                                                        | Inte                                  | r-record gap is related to      | o which  | one o | the following storage devices? |

| •  |                                                                           | a)                                    | Floppy Disk                     | •        | b)    | Hard Disk                      |

|    |                                                                           | c)                                    | CD-ROM                          |          | d)    | Magnetic Tape.                 |

|    | vi) Which of the following registers holds an instructon until it is deco |                                       |                                 |          |       |                                |

|    |                                                                           | a)                                    | Index Register                  |          | b)    | Memory Address Register        |

|    |                                                                           | <b>c</b> )                            | Instruction Register            |          | d)    | Data Register.                 |

11019 (5/12)

| CA/SE | M-1/N | MCA-101/08/(09)             | 4            |                            |                   |

|-------|-------|-----------------------------|--------------|----------------------------|-------------------|

| vii)  | Gat   | ed D latch is called        | latc         | h.                         |                   |

|       | a)    | Transport latch             | <b>b</b> )   | Traverse latch             |                   |

|       | c)    | Transparent latch           | d)           | Nested latch.              |                   |

| viii) |       | bulk storage, which one     |              | owing storage devices is n | nost suitable     |

|       | a)    | Hard Disk                   | b)           | Magnetic Tape              |                   |

|       | c)    | CD-ROM                      | d)           | DVD.                       |                   |

| ix)   | INT   | R is an interrupt signal o  | of           | priority.                  |                   |

|       | a)    | highest                     | b)           | lowest                     |                   |

|       | c)    | medium                      | <b>d</b> )   | same.                      |                   |

| x)    | Wh    | ich one of the following op | erations is  | not performed by ALU?      |                   |

|       | a)    | Clear                       | <b>b</b> )   | Floating point calculation | 1                 |

|       | c)    | Logical OR                  | d)           | Logical AND.               | , .               |

|       |       |                             |              |                            |                   |

| •     |       |                             | GROUP - B    |                            |                   |

|       |       | ( Short Ans                 | wer Type Q   | uestions )                 |                   |

|       |       | Answer any                  | three of the | e following.               | $3 \times 5 = 15$ |

- Design a half adder circuit using minimum number of 2-input NOR gates only. Write 2. down the truth table and Boolean function also.

- Convert a JK flip-flop to a D flip-flop. You can use additional circuitry, if required. 3.

- Construct a  $5 \times 32$  decoder with the help of  $2 \times 4$  decoders. Show the block diagram 4. only.

- Write short notes on any one of the following: 5.

- i) Universal gate

- Master-Slave JK flip-flop ii)

- iii) Cache Memory.

- Obtain the POS form of F ( A, B, C, D ) =  $AB\overline{C} + A\overline{D} + CD$ . 6.

# 11019 (5/12)

#### GROUP - C

#### (Long Answer Type Questions)

Answer any three questions.

$3 \times 15 = 45$

- 7. a) Prove that  $(a + b' + c')' \cdot (ab' + abc) = 0$  in Boolean algebra.

- b) Why does 11 come before 10 in the Karnaugh map?

- c) How many input line(s) and selection line(s) must be present in a demultiplexer that has 32 possible output lines?

- d) Why is a gated D latch called 'transparent' latch?

- e) Design a combinational circuit using different logic gates that can convert BCD code to its corresponding Excess-3 code. 2 + 2 + 1 + 2 + 8 = 15

- 8. What is pipeline architecture? What is speed-up, efficiency and throughput of a pipe-lined architecture with reference to non-pipelined architecture. What is locality of reference? Write down the various ways in addressing cache. Write down the difference between direct, indirect and implicit address instructions.

$$2 + 3 + 2 + 5 + 3 = 15$$

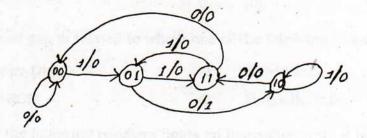

Design a sequential circuit using JK flip-flop which realizes the following scale diagram:

- b) Draw a schematic diagram of Master-Slave JK flip-flop.

- c) Find out the Q value of R if  $(125)_R = (203)_5$ .

8 + 4 + 3 = 15

11019 (5/12)

6

- 10. a) Show how two 4: 1 MUX can be connected to provide an 8:1 MUX.

- b) Design a mod 8 synchronous counter.

- c) What is vector processing?

5 + 5 + 5 = 15

- 11. a) Design  $16 \times 4$  bit RAM using  $4 \times 2$  bit RAM IC modules.

- b) What is the difference between memory mapped I/O and I/O mapped I/O?

- c) Briefly explain arithmetic & logic instructions.

6 + 4 + 5 = 15

Write short notes on any three of the following:

$3 \times 5 = 15$

- a) Self-complementing property of Excess-3 code

- b) DMA controller

12.

- c) von Neumann architecture

- d) Addressing modes.

**END**